# CMP 中の low-k 材料界面のはく離可能性の予測方法

### Estimation on the Probability of Delamination at Low-k Interfaces during CMP Processes

by Yoshihiro MOCHIZUKI, Hideki SHIBATA, Manabu TSUJIMURA, & Hirokuni HIYAMA

An estimation was done on the probability of delamination at low-k interfaces during CMP (Chemical Mechanical Planarization) processes. This was done by carrying out 4-point bending and delamination tests during CMP, mapping the relationship between the two test results in terms of stress distribution in an interconnect structure, and estimating the mechanical property of the device. It was revealed that if the value of Young's modulus of low-k material at the trench part of the interconnect structure is above a certain value, an extremely low CMP downforce becomes unnecessary. It was also revealed that the combination of material is an important factor for reducing delamination.

Keywords: Chemical Mechanical Planarization, Low-k material, Delamination, Finite element method, Fracture mechanics

### 1. はじめに

近年の超LSI(大規模集積回路)素子では,素子内部での電気信号の伝播遅延時間を低減するために,低誘電率(low-k)の層間絶縁膜と銅配線(Cu配線)を用いた多層配線プロセスが標準的な製造方法の一つとなっている。また,無機系の材料を多孔質にしたり有機系の材料を用いて,更に低誘電率化したlow-k材料の層間絶縁膜への導入が始まっている。これらの先端low-k材料は機械的強度が著しく低いため,LSI素子の製造工程中に作用する応力によって素子に様々な損傷が生じる可能性があることが指摘されている「~3)。このような損傷のうちlow-k膜のはく離は,パッケージング時やボンディング時に作用する圧縮応力や衝撃力,製造工程上で必要な熱履歴による熱応力,CMP(化学的機械研磨)中に作用する応力など発生要因が多岐にわたるため,次世代LSI素子配線の製造上の重要な課題の一つと考えられる4~7)。

\* ㈱荏原総合研究所 物理研究室 工学博士

はく離は界面に沿って亀裂が進展する破壊現象の一種であるため、LSI素子配線のはく離の発生の予測にも破壊力学の指標を用いることができると考えられる。本論文では、破壊力学的な測定結果とCMPのはく離確率の測定結果の関係を数値解析で容易に求められる応力分布に写像する手法と、それを用いた将来のCMP中でのlow-k材料界面でのはく離確率(すなわち破壊確率)を予測する手順を示し、将来のLSI配線でのはく離防止の観点からの留意点を考察した<sup>8,9</sup>。

## 2. CMP中のLSI素子配線のはく離解析の 考え方

### 2-1 LSI素子配線のCMP中のはく離解析の問題点

破壊力学では破壊強度の評価方法として何種類かの指標が提案されているが、LSI素子材料の測定結果の多くは、部材内のエネルギーに基づいた破壊力学の指標、すなわち「エネルギー開放率G>破壊靭性Gc」 $^{*1}$ を用いている $^{5\sim12}$ 。この不等式の左辺は部材内部の欠陥(亀裂)の周りに蓄積されているエネルギーであり、右辺は

\*\*1 破壊靭性Gcは,厳密には「臨界エネルギー開放率」であるが、エネルギー開放率Gと区別し難いため,本論文では,ほぼ等価な意味の破壊靭性の言葉を用いている。

<sup>\*\* (</sup>株)東芝 セミコンダクター社 工学博士

<sup>\*\* ㈱</sup>精密・電子事業カンパニー CMP装置事業部 工学博士

<sup>\*\* (</sup>株) 在原総合研究所 工学博士

測定によって求める材料固有の値である。この指標は, 亀裂周辺に蓄えたエネルギー(左辺G)がある許容値 (右辺Gc)を超えると,材料が耐えられなくなって亀裂 が進展し始めることを意味している。概念的には明快で 実用性もある指標であるが,将来のLSI素子配線の強度 予測に用いようとすると,G,Gc の値を求める際に困難 が生じる。

エネルギー開放率 Gを求める際の問題は、Gの算出方法である。エネルギー開放率 Gは、同じ負荷条件に対する「亀裂がない部材に蓄積された歪エネルギー密度」と「亀裂の周辺に蓄積された歪エネルギー密度」の差分であり、亀裂の成長によって開放され、亀裂に与えられるエネルギーに対応する。エネルギー開放率 Gを求めるためには、亀裂がある場合と亀裂がない場合の両方の応力場を算出する必要がある。このため、理論的な解析では試験片のような非常に単純な形状の部材以外では解析解を得ることは難しい。また、数値解析によっても、三次元構造をもつ LSI 配線のような複雑な構造の場合には解析モデル作成に著しい困難がある。

破壊靭性 Gc を求める際の問題は、Gc が材料固有の値であるので、既存の材料でなくては求めることができないことである。既存の材料の間での相対的な比較では、破壊靭性 Gc は有効な指標であるが、将来のLSI素子の配線材料に対しては何らかの推定が必要である。また破壊靭性の測定では、あらかじめ理論解析で得られた試験片のエネルギー開放率の理論式を基に、亀裂が生じた時点の負荷条件から逆算する。左辺の問題で述べたように、三次元構造をもつLSI素子配線ではエネルギー開放率の理論式を求めることは困難なので、実際的な素子形状をもつ試験片を使って測定することはできないという問題もある。

#### 2-2 計算の簡単化

まず、Gの算出の簡単化について検討する。前述のように、エネルギー開放率の計算は技術的な難があるが、内部に亀裂を有しないLSI配線の「歪エネルギー密度W」は、有限要素法の応力分布を用いれば比較的簡単に計算できる。エネルギー開放率Gは「亀裂が存在するときの歪エネルギー密度」と「亀裂が存在しないときの歪エネルギー密度」の間の差分であるから、初期亀裂と応力状態がある程度同じであるなら、エネルギー開放率Gはおおむね歪エネルギー密度Wに比例すると考えられる。この仮定が成り立つ範囲であれば、歪エネルギー密度Wからエネルギー開放率Gへのある"換算率(scaling factor)"を何らかの方法で求めることで、LSI素子のよう

な複雑な形状では算出が困難なエネルギー開放率Gの替わりに,算出が容易な歪エネルギー密度Wを用いることができる。次項で示す手順では,既知の数点の実験結果と有限要素解析結果の比較から"換算率(scaling factor)"を得る方法を示す。

Gc に議論を転じると、破壊靭性 Gc は材料固有の値であるので、材料の基本的な組成も決まっていない将来のLSI素子材料に対して理論的な値を得ることは事実上不可能である。したがって、推定できる他の物性値に基づいた実験式によって推測することしかできない。ここでは、著者らが考案した将来のLSI素子材料の誘電率の要求値から将来のLSI素子材料の弾性率を推定する方法<sup>13)</sup>を利用して、弾性率を基にして破壊力学的なパラメータを含んだ実験式を考案した。ここで推定するのは、試験片を用いた実験で得られる破壊靭性である。

前記の考え方に基づき、将来のLSI素子配線のCMP中のはく離の確率を推定した。以下の節で、詳細な手順と推測結果を述べる。

### 3. 具体的なはく離確率の推定方法

LSI素子配線のCMP中でのはく離確率の推定の手順 は四つのステップに大別される。以下、それぞれ手順を 具体的に示す。

## 3-1 歪エネルギー密度Wからエネルギー開放率への 換算係数を定めるステップ

このステップでは、数種の材料の組合せに対して、 CMP中のはく離実験の結果と四点曲げ試験の試験結果 を用いて"換算率 (scaling factor)"を得る。

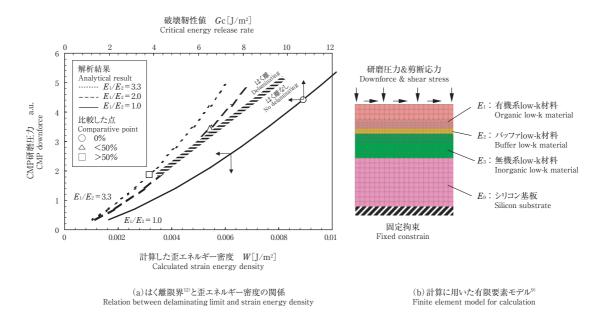

まず、各種の試験片に対して破壊靭性とCMP研磨圧 力の関係を測定した。種々のlow-k材料を積層した試験 片をプロセス条件や材料を変えて作成し、破壊靭性 Gc を四点曲げ試験によって測定した。次に, 各々の試験片 と同じ材料の組合せのパターンなしのウェーハを用い, CMPの研磨圧力をパラメータとしてCMPを行い、はく 離面積を求めた<sup>12)</sup>。図1(a)中の斜線の線は、横軸を四 点曲げ試験で得られた破壊靭性(上),縦軸をCMP研磨 圧力 (右) として描いた CMP 中のはく離限界線である <sup>12)</sup>。 一方、3種類の材料の組合せについては、ナノインデン テーション評価によって成膜された材料の弾性率を測定 し、またCMPによるはく離面積を求めた。この3種の 弾性率を測定した試験片(弾性率の比 $E_1/E_2$ =3.3, 2.0, 1.0で表す)の組合せと同じ有限要素解析モデル [図1 (b):中央部だけ抜粋表示]を作り、その解析モデルに 研磨圧力と摩擦力起因の剪(せん)断応力を境界条件と

図1 計算と実験結果の"換算率"を求める図と計算に用いた解析モデル

Fig. 1 Graph for obtaining the "scaling factor" between calculation and experimental results, and analysis model for the calculation

して与えてlow-k材料界面での歪エネルギー密度を解析した。図1 (a) 中の実線、破線、点線は、有限要素解析で得られたそれぞれの試験片に対応する CMP中の歪エネルギー密度である [横軸は歪エネルギー密度 (下)]。この解析では、CMPパッドとウェーハの真実接触面積の測定結果 $^{14}$  とヘルツ接触を考慮した真実接触面積の関係 $^{15}$  を用いて、ウェーハ裏面全体に作用する圧力ではなく、CMPパッドとウェーハが接触している部分に局所的に作用している圧力を境界条件として与えている。

なお、破壊靭性(横軸:上)は、材料固有の値である ので、ある特定の試験片では一定でありはく離限界線上 ではエネルギー開放率は破壊靭性となるが、この場合に は四点曲げ試験とCMPでは負荷条件(すなわちはく離 発生点周辺の応力条件)が異なるので、対応関係はあっ ても必ずしも一致はしない。

一方,図1(a)中の〇△□印は,歪エネルギー密度を求めた三つの試験片のはく離面積と四点曲げ試験による破壊靭性 Gc を示している。図1(a)は,この三つの試験片のはく離面積が対応するように上下の横軸を調整した結果である。図1(a)から"換算率(scaling factor)"を G=1200 Wと決定した。

## 3-2 将来のLSI素子の配線構造と材料特性を決める ステップ

本論文では、ITRS2004 update<sup>16)</sup>を参考にして、80 nm

ノードから 18 nm ノードまでを対象として将来のLSI配線構造の寸法と誘電率kを決定した。

今回の解析では、図2の構造模式図に示す、配線溝部(trench)の有機系low-k膜の上にハードマスク(HM)をもち、via部周辺の層間絶縁膜は無機系low-k膜であるハイブリット構造のLSI配線構造を仮定した。また、図2の各部に対応する寸法を表に示す。配線溝部の銅配線は、図2から見て奥行き方向に延びているが、via部の銅配線は、配線溝部とその下の図示しない下層部分とを連結する概円柱状の部材である。また、銅配線の周り(low-kとCuとの間)には、銅が層間絶縁膜に拡散することを防止する、いわゆるバリア膜を考慮した。このようにLSI配線の一部の構造を見ても、単純ではない三次元的な構造をしている。

配線構造の層間絶縁膜の誘電率kは、ITRS2004 update $^{16}$ )の各テクノロジーノードごとに要求される誘電率を満たすように定め、それぞれの部分に対応する弾性率Eを弾性率の相関関係 $^{13}$ )から推定した。本論文では、将来のLSI配線に用いられるlow-k材料の弾性率が図3に示すような推移となる3ケースを仮定した。すなわち、ケース1:有機系low-k材料も無機系low-k材料もk-値の減少に伴って線形に減少するケース、ケース2:有機系low-k材料も無機系low-k材料もk-値にかかわらず一定のケース、ケース3:有機系材料(配線溝部)だ

Fig. 2 Sectional schematics of discussed interconnect architecture

図3 想定したヤング率の推移 Fig. 3 Progress of assumed Young's modulus

表 世代ごとの配線の寸法の推定値(単位:nm) **Table** Estimated values of dimensions of interconnect architectures for each generation (unit:nm)

| 年<br>Year                        |                 | 2005  | 2007 | 2009 | 2012 | 2015 | 2018 |

|----------------------------------|-----------------|-------|------|------|------|------|------|

| DRAM1/2ピッチ<br>DRAM 1/2 pitch     |                 | 80    | 65   | 50   | 35   | 25   | 18   |

| 銅拡散防止膜<br>Cu.D.B.                | 高さ<br>height    | 50    | 35   | 30   | 20   | 15   | 10   |

| ハードマスク<br>Hardmask               | 高さ<br>height    | 50    | 40   | 35   | 20   | 15   | 10   |

| Via                              | 直径<br>dia.=M1   | 100   | 70   | 50   | 35   | 25   | 18   |

|                                  | 高さ<br>height    | 150   | 112  | 80   | 60   | 43   | 32   |

| 配線溝<br>Trench                    | 幅<br>width      | 114.8 | 80.4 | 57.4 | 40.2 | 28.8 | 20.6 |

|                                  | 高さ<br>height    | 170   | 126  | 90   | 67   | 48   | 36   |

| 最小ライン/スペース<br>Minimum line/space |                 | 100   | 70   | 50   | 35   | 25   | 18   |

| バリア<br>Barrier                   | 厚さ<br>thickness | 7.4   | 5.2  | 3.7  | 2.6  | 1.9  | 1.3  |

け、65 nmノード以降は一定値になるケースである。これらのケースは、それぞれケース1:k-値の減少に伴って低下する材料強度に対して何ら対策を施さない場合、ケース2:k-値が下がっても全く強度低下しない理想的な場合、ケース3:k-値が下がってもある一定以下の弾性率にならないように対策を施した場合を想定したものである。

### 3-3 特定の材料の組合せに対する破壊靭性 *Gc* を推測 するステップ

特定の材料の組合せに対する破壊靭性Gcをステップ

3-2で決定した弾性率から推定する。

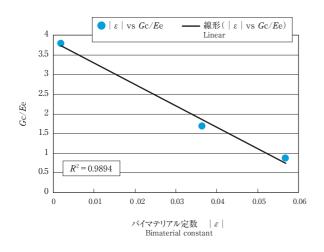

まず、均質な材料を考えてみると、脆性材料であれば破壊靭性 Gc は大まかには弾性率に比例すると考えられる。一方、二つの材料の界面に沿ったエネルギー開放率 G は、二つの材料の等価な弾性率 Ee とバイマテリアル定数(bi-material constant)  $\varepsilon$  の関数となることが知られている  $^{17}$ 。このため、材料界面の破壊靭性 Gc も二つの材料の等価な弾性率 Ee とバイマテリアル定数  $\varepsilon$  で表されると仮定した。破壊靭性 Gc と弾性率が既知の三つの材料の組合せに対して種々の実験式を試した結果、

Gc=

$$a$$

(1 -  $b$  |  $\varepsilon$  | ) Ee

1/Ee = (1 -  $\nu_1^2$ ) / $E_1$  + (1 -  $\nu_2^2$ ) / $E_2$

$\varepsilon$  = ln [(1 - $\beta$ ) / (1 - $\beta$ )]

なる形式を得た。ここに、 $E_1$ ,  $E_2$ ,  $\nu_1$ ,  $\nu_2$  は各々の添え字に対応する材料の弾性率とポアソン比、 $\beta$  はダンダースパラメータ(Dunder's parameter)と呼ばれる二つの材料の弾性率とポアソン比のミスマッチを表すパラメータ<sup>17)</sup>である。**図4** は前記の関係式を材料特性値が既知の試験片のデータについて表した結果で、上式の定数 a とb は図4の傾き及び切片から求めることができる。

#### 3-4 解析ステップ

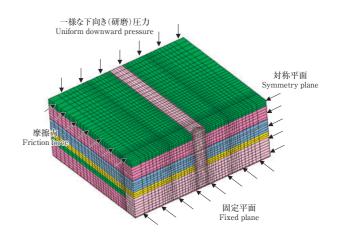

ステップ3-1からステップ3-3の操作により、CMPによって平坦化される間にはく離の発生確率を求める計算を行う準備が整う。ステップ3-2で推測した将来のLSI配線材料の弾性率と寸法を用いてLSI配線構造に作用する応力場を有限要素法で計算した。材料界面の歪エネルギー密度Wは応力場から計算する。図5は解析に用いたLSI配線の有限要素解析モデルの一例で、1層のデュアルダマシン(dual damascene)構造とその下の配線部(trench)をふくむ1.5層の孤立配線構造を仮定したものである。

via 部の中心に沿った平面を対称平面,モデルの底面を 拘束面とし,3.45 kPa (0.5 psi)のCMP研磨圧力に対応 する局所圧力と摩擦(摩擦係数0.43)による剪断応力を 境界条件とした。汎用構造解析ソフトMSC/Marc 2005を 用いて解析モデルの応力分布を計算し,はく離の評価点 として,Cu配線の外側の直近の層間絶縁膜(2種の層間 絶縁膜の界面)の歪エネルギー密度Wの値を求める。

求めた歪エネルギー密度Wをステップ3-1で求めた

図4 破壊靭性の実験式の定数を求める図 **Fig. 4** A chart to obtain the constants of empirical formula of

fracture toughness

図5 配線構造の計算に用いた有限要素モデル Fig. 5 Finite element model for the calculation of inter-connect architecture

"換算率(scaling factor)"によってエネルギー開放率の推定値G'に変換する。また評価点の界面を構成する材料の弾性率やポアソン比を用いて,ステップ 3-3 の関係式から,この時の破壊靭性の推定値Gc'を求め,エネルギー開放率との比G'/Gc'を求める。ここに ' は推定値の意味である。比G'/Gc'が1を超えると,はく離発生の可能性が高いと考えられる。

### 4. 推定の結果及び考察

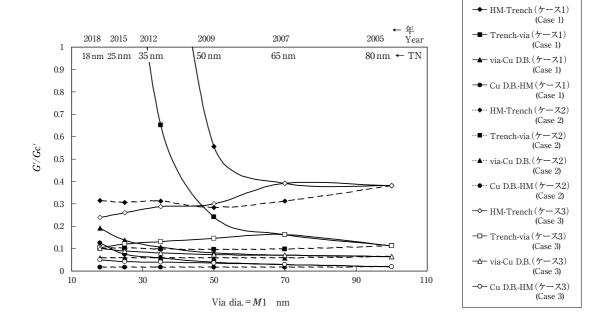

図6は、CMP研磨圧力を3.45 kPa(0.5 psi)とした時の材料界面でのはく離の可能性を推測した結果を、via部の直径(= いわゆるM1 寸法)を代表寸法として示したものである。

ここで、HM-Trenchは、図2のハードマスクと有機 low-k 膜の界面、Trench-via は有機 low-k 膜と無機 low-k 膜の界面、via-Cu.D.B は有機 low-k と銅拡散防止膜の界面、Cu.D.B.-HM は図2の一番下の銅拡散防止膜と図示していない下の層の一番上のハードマスクとの界面を示している。

ケース1では65 nmノード(2007年)までは大きな変化はなく、また3.45 kPaの裏面圧力では35 nm(2012年)までははく離しないことが分かる。弾性率の変化がないケース2でもM1の変化に対して若干の変動があるが、これは寸法の縮小に伴うlow-k膜厚みの比やアスペクト比の変化の効果である。ケース3では65 nmノード(M1=70 nm)以降で全般に $G'/G_{C}'$ は低下し、35 nmノード以降ではむしろケース2よりも下回る。

ここで、80 nm ノード(M1=100 nm)のHM-Trench 間のG'/Gc'を、局所圧力と裏面圧力の関係からCMP研

図6 CMP中のはく離確率の推定結果 Fig. 6 An estimation result of delaminating probability during CMP

磨圧力が13.8 kPa (2 psi) の場合になるように換算する と0.95になる。実際に80 nmノードのLSI配線の場合, 13.8 kPaより大きなCMP研磨圧力で,しばしばはく離が発生することが知られており,ある程度実際のはく離限界と対応していることが分かる。

さて、前述の推定結果は、ステップ3-1で求めた"換算率(scaling factor)"とステップ3-3の破壊靭性の実験式から導かれている。よく知られているように、界面の材料特性は接着剤、表面粗さ、結晶方向、粒径などに影響を受け、これらのパラメータは主に薄膜の製造工程に依存する。このため、この推測方法によってはく離の可能性を量的に比較するためには、本来、類似の製造工程によるものを用いなくてはならない。他の製造工程による場合には大きな推測誤差が含まれる可能性がある。この意味では、有機low-k材料と無機low-k材料の組合せを用いている、HM-Trench間とTrench-via間だけの結果がある程度妥当であることに注意する必要がある。その他の組合せを、相互に比較すると誤った評価になる可能性がある。

しかしながら、HM-Trench間のはく離の可能性から、 材料の組合せの影響がはく離を防止するのに重要である ことが分かる。35 nmノード以降ではより柔らかいlow-k 材料 (ケース3) は、より硬い材料 (ケース2) よりも低 い確率を示している。これは、ケース3では有機系low-k 材料と無機系low-k材料の弾性率の比が小さくなったことにより、材料界面での応力集中が緩和されているからだと考えられる。

更に、この推測結果は、もしtrench 部の有機low-k 膜の弾性率が維持されたなら、 $18 \, nm$  J ード( $M1=18 \, nm$  and year 2018)まで極端に低い<math>CMP圧力は必要がないことを示唆している。

### 5. おわりに

low-k材料の弾性率の推移を考慮したはく離耐性の一推測を示した。本論文ではITRS2004 updateの2005年から2018年の間のCMP中のはく離の可能性を議論した。ハイブリッド構造においては、3.45 kPa (0.5 psi)のCMPダウンフォースを用いても、誘電率の低下に伴って低下する弾性率に何らの対策をしない低強度の材料を用いた場合(ケース1)には、2012年にはく離による製造限界が生じる可能性がある。しかし、配線溝周辺の層間絶縁膜の弾性率がある程度より小さくならないように配慮した場合(ケース3)には、将来にわたっても、はく離耐性は劣化しないことが示唆されている。

なお、本論文は米国Material Research SocietyのADMETA2006 Asian Sessionで発表し、同会の論文集に投稿した論文<sup>9)</sup> を日本語に改めて加筆修正したものである。

#### 参考文献

- 1) 柴田英毅,高性能SoCにおけるCu/Low-k多層配線プロセス インテグレーションの課題と展望,2004年度精密工学会秋季 大会学術講演会講演論文集,p.477-478.

- 2) 大崎明彦,多層配線技術の動向, Proc. SEMI Technology Symposium 2004 (SEMICON Japan 2004), p.5-6.

- M. Kodera et al., Journal of The Electrochemical Society, 152 (6), G506, (2005).

- A. Namiki, et al, Cu-CMP中の摩擦とポーラスLow-k膜の剥離に関して,第43回プラナリゼーションCMP委員会研究会資料(2005年4月14日), p.48-59.

- Ting Y. Tsui, et al, "Effects of Elastic Modulus on the Fracture Behavior of Low-Dielectric Constant Films", Proceedings of the 2005 IEEE IIITC.

- (6) 清野豊, Low-k 膜の密着性評価技術,2004年半導体MIRAIプロジェクト成果報告会(2004.07.13).

- Z. Gan, et al, Study of interfacial adhesion energy of multilayerd ULSI thin film structures using four-point bending test, Surface & coating Technology, 198, p.85-89 (2005).

- 8) 望月宣宏・柴田英毅・辻村学・檜山浩國, CMP中のLow-k 材料界面に作用する応力解析, 日本機械学会関東支部第12回総会講演会講演論文集, p.51-52 (2006).

- Y. Mochizuki, H. Shibata, M. Tsujimura, H. Hiyama, "Stress analysis of low-k material interface during CMP", in ed. by S. W. Russell et al, "Advanced metallization conference 2006 (AMC2006)", p.383-388, Material Research Society (2007).

- 10) 小久保輝一・高橋要子・山中達也, MSQ low-k膜の機械物性 の改善, Proc. SEMI Technology Symposium 2005 (SEMI-CON Japan 2005), p.2-32.

- 11) R. H. Dauskardt, et al, Adhesion and debonding of multilayer thin film structure, Engineering Fracture Mechanics, 61, p.141-162 (1998).

- T. Nishioka, et al, Extendibility of CMP Process to Cu/p-Low-k Interconnect Fabrications, Proc. 2006 CMP-MIC Conference, p.73-78 (2006).

- 13) Y. Mochizuki, H. Shibata, M. Tsujimura, H. Hiyama, Finite element Analysis of the Stress in Vias With Cu/Low-k Structure, in ed. by S. H. Brongersma, "Advanced Metallization Conference 2005 (AMC 2005)", p.673-678, Material Research Society (2006).

- 14) 三橋真成・小野秀之・磯部晶, CMPによる平坦化研磨―パッドとウェハの接触状況―, 1995年度精密工学会秋季大会学術講演会講演論文集, p.20-21.

- 15) J. Luo & D.A.Dornfeld, Integrated Modeling of Chemical Mechanical Planarization for Sub-Micron IC Fabrication-From Particle Scale to Feature, Die and Wafer Scales-, Springer-Verlag (2004), p.62.

- International Technology Roadmap for Semiconductors, 2004 update edition, Interconnect, ITRS.

- 17) 結城良治編著, 界面の力学, 培風館 (1993).